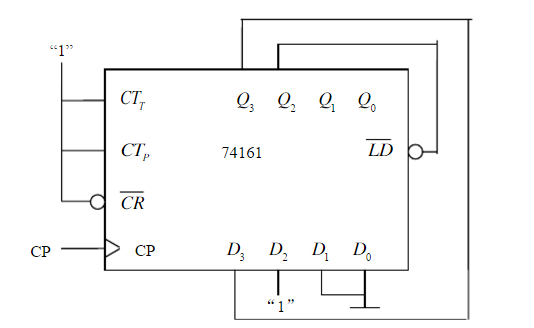

更多“试分析如图所示由4位二进制同步计数器74161组成的电路。”相关的问题

更多“试分析如图所示由4位二进制同步计数器74161组成的电路。”相关的问题

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

由16×4位ROM和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-13所示,ROM输入和输出关系如表7-4所示。试画出在CLK信号作用下D3、D2、D1、D0的波形。

表7-4 R0M输入和输出关系 | |||||||

| 地址输入 | 数据输出 | ||||||

| A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 1 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 | 1 0 0 1 1 0 0 0 1 1 0 0 0 1 1 0 | 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 | 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

A.由32位二进制数组成

B.每8位为一组,用小数点“.”分隔

C.每4位为一组,用小数点“.”分隔

D.每组用相应的十进制数(0-255之间的正整数)表示

A.由同类型的触发器构成

B.各触发器时钟端连在一起,统一由系统时钟控制

C.可用前级的输出做后级触发器的时钟

D.可用后级的输出做前级触发器的时钟

如图所示为一乘积型同步检波器,假如本地恢复载波v'c(t)(即同步信号)为v'c(t)=cos[(ωc+ωε)t+φε],式中ωε为频率误差,φε是相位误差。试求:vs(t)分别为下列信号时,检波器输出vD(t)的表示式,并说明能否实现无失真解调;什么情况下能实现无失真解调。

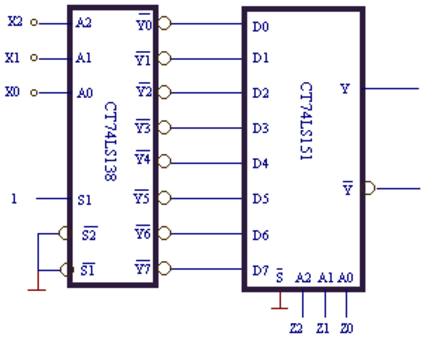

由3线-8线译码器CT74LS138及8选1数据选择器CT74LS151组成电路如下图所示。X2X1X0及Z2Z1Z0为两个3位二进制数。试分析电路的逻辑功能。

用两片4位数值比较器74HC85实现三个4位二进制数A=A3A2A1A0,B=B3B2B1B0,C=C3C2C1C0的并行比较。要求给出“A最大”、“A最小”和“三个数相等”三个输出信号,必要时可用门电路。

如果结果不匹配,请

如果结果不匹配,请