题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

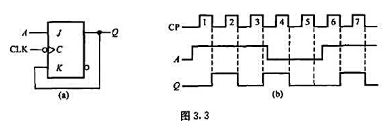

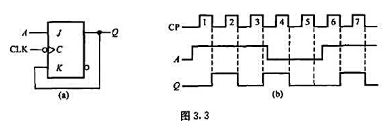

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.已知电路CLK和A的输入波形如图3.3(b)所示.设Q输出初态为0,画出Q的波形.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.…”相关的问题

更多“JK触发器组成图3.3(a)所示电路.试分析电路的逻辑功能.…”相关的问题

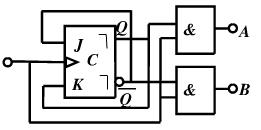

图13.11(a)所示是用JK触发器组成的双相时钟电路。若CP端加上时钟脉冲信号,在输出端可得到相位互相错开的时钟信号A和B,试画出Q, 和A,B的波形,假设触发器的初始状态为0。

和A,B的波形,假设触发器的初始状态为0。

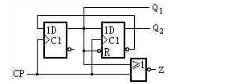

图题4.18所示是用CMOS边沿触发器和或非门组成的脉冲分配电路。试画出在一系列CP脉冲作用下Q1、Q2和Z端对应的输出电压波形。设触发器的初始状态为Q=0。

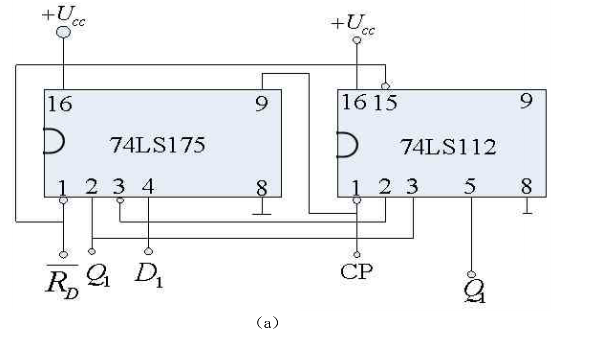

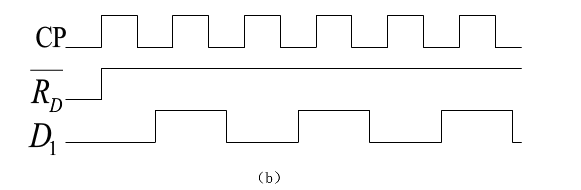

74LS175型四上升沿D触发器和74LS112型双下降沿JK触发器的接线图如图 21.40(a)所示,它们的外引线排列分别见教材图21.6.4(b)和教材图21.11(b)。(1)试按图画出逻辑电路;(2)设CP, ,D1的波形如图21.40(b)所示,试画出两触发器输出端Q的波形。两触发器的初始状态均为0。

,D1的波形如图21.40(b)所示,试画出两触发器输出端Q的波形。两触发器的初始状态均为0。

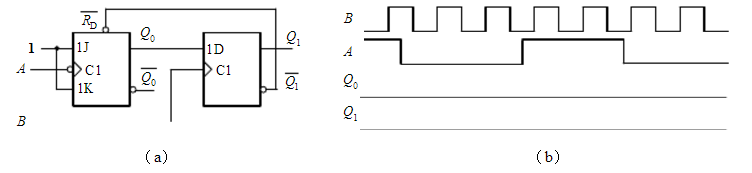

由JK触发器和D触发器构成的电路如图P4.12(a)所示,各输入端波形如图P4.12

(b),当各个触发器的初态为0时,试画出Q0和Q1端的波形,并说明此电路的功能。

由JK触发器组成的电路如图所示,试写出电路的状态方程,并画出在

CP作用下Q1、Q2、

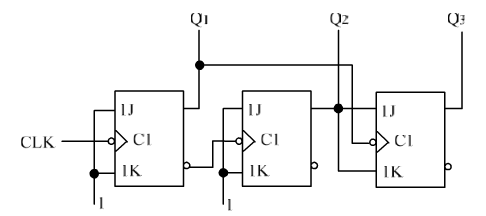

试画出图5.26.1所示电路在一系列CLK信号作用下Q1、Q2、Q3端输出电压的波形。触发器均为边沿触发方式,初始状态为Q=0。