题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

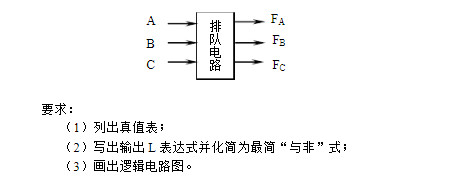

一个排队线路,输入为A、B、C,其输出分别为FA、FB、FC,在同一时间内只能有一个信号通过.如果同时有两个或两个以

一个排队线路,输入为A、B、C,其输出分别为FA、FB、FC,在同一时间内只能有一个信号通过.如果同时有两个或两个以上输入,则按A、B、C的顺序输出.例如,A、B、C同时输入时,只能A有输出.写出FA、FB、FC的逻辑表达式,并化成全功能集{↓}中的表达式。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

一个排队线路,输入为A、B、C,其输出分别为FA、FB、FC,在同一时间内只能有一个信号通过.如果同时有两个或两个以上输入,则按A、B、C的顺序输出.例如,A、B、C同时输入时,只能A有输出.写出FA、FB、FC的逻辑表达式,并化成全功能集{↓}中的表达式。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“一个排队线路,输入为A、B、C,其输出分别为FA、FB、FC…”相关的问题

更多“一个排队线路,输入为A、B、C,其输出分别为FA、FB、FC…”相关的问题

试设计一个三线排队电路,采用3线-8线译码器74138实现。其功能是输入信号A、B、C通过排队电路后,分别由FA、FB、FC输出,且在同一时间只能有一个信号通过。如果同时有两个或两个以上的信号出现,则输入信号按A、B、C的优先顺序通过。

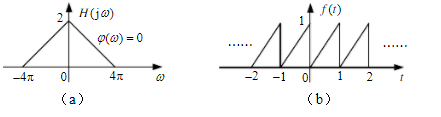

一个理想滤波器的频率响应如图(a)所示,其相频特性为φ(ω)=0。若输入信号为图b的锯齿波,求输出信号()yt。

对于稳定的因果系统,如果输入一个频率为ω0的复正弦序列 ,则其输出为y(n)=______,设系统的频率响应H(ejω)已知。

,则其输出为y(n)=______,设系统的频率响应H(ejω)已知。

设计一个时序电路,只有在连续两个或两个以上时钟作用期间,两个输入信号X1和X0一致时,输出信号才是1,其余情况输出为0。

优先,B次之,C更次之,即当A,B,C同时为1时,电路选取A;若A=0,B=1,C=1,则选择B,其余类推。用Verilog HDL完成电路的设计。

设计一个波形发生器,其输入为CP脉冲,输出Z的波形如图7.3.27所示。 (1)用触发器和门电路完成上述设计。 (2)试用MSI移存器74LS195和门电路完成上述设计。 (3)用VHDL语言完成上述设计。

1.jpg)

股份大小决定的输出表决结果:赞成、平局和否决,分别用F1、F2和F3表示。(股东投票赞成和输出表决结果均用1表示)。

设计一个温度控制电路。其输入为4位二进制数T3T2T1T0,代表检测到的温度。输出为X和Y,分别用来控制暖风机和冷风机的工作。当温度低于5时,暖风机工作,冷风机不工作;当温度高于10℃时,冷风机工作,暖风机不工作;当温度介于5℃和10℃之间时,暖风机和冷风机都不工作。用1表示暖风机和冷风机工作,用O表示暖风机和冷风机不工作。用与非门实现电路。