题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

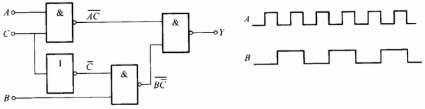

在图20.31(a)的门电路中,当控制端有C=1和C=0两种情况时,试求输出Y的逻辑式和波形,并说明该电路的功能。输入A

在图20.31(a)的门电路中,当控制端有C=1和C=0两种情况时,试求输出Y的逻辑式和波形,并说明该电路的功能。输入A和B的波形如图中所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

在图20.31(a)的门电路中,当控制端有C=1和C=0两种情况时,试求输出Y的逻辑式和波形,并说明该电路的功能。输入A和B的波形如图中所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“在图20.31(a)的门电路中,当控制端有C=1和C=0两种…”相关的问题

更多“在图20.31(a)的门电路中,当控制端有C=1和C=0两种…”相关的问题

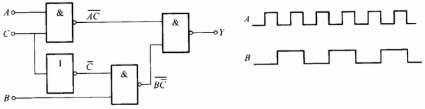

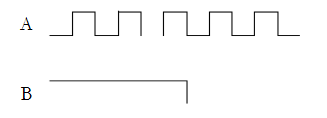

如果与门的两个输入端中,A为信号输入端,B为控制端。设输入A的信号波形如图20-19所示,当控制端B=1和B=0两种状态时,试画出输出波形。如果是与非门,或门,或非门则又如何,分别画出输出波形。最后总结上述四种门电路的控制作用。

发器和门路电路(门电路类型不限)实现,画出最简逻辑图,并验证能否自启动(若不能自启动,不必修改成自启动电路)。

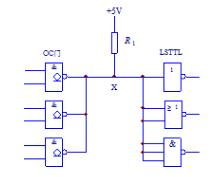

图P3.7中的门电路全部是LSTTL电路,其中OC门输出端高电平漏电流IOZ≤100μA,输出低电平VOL≤0.4V时最大负载灌电流ILM≤8mA;门的输入电流IIL≤-0.2mA,IIH≤20μA。如果要求X点(即负载门的输入端)高、低电平分别为VIH≥3V,VIL≤0.4V,请计算上拉电阻R1的选择范围。

图(a)所示电路中,NR为线性无源电阻网络,当输入端1-1'接2A电流源时,测得输入端电压为10V,输出端开路电压为5V;若把电流源接在输出端,同时在输入端接5Ω电阻,如图(b)所示,分别用特勒根定理和互易定理求流过5Ω电阻的电流i为多少?

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

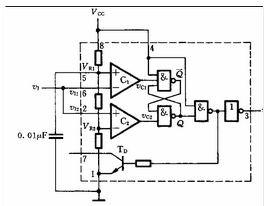

在图题6.18用555定时器接成的施密特触发器电路中,试求:

(1)当Vcc=12V,而且没有外界控制电压时,求VT+、VT-及△VT值。

(2)当Vcc=9V,外接控制电压Vco=5V时,VT+、V-、△VT各为多少?

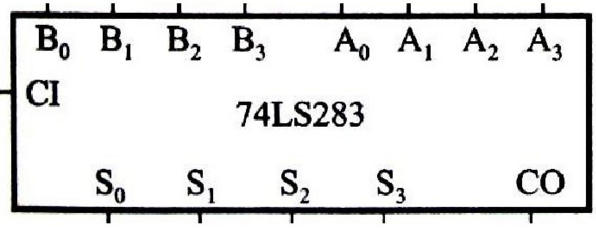

试用4位并行加法器74LS283设计一个加/减运算电路。当控制信号K=0时将两个输入的4位二进制数相加,而K=1时它将两个输入的4位二进制数相减,允许附加必要的门电路。

试用四位并行加法器74LS283设计一个加/减运算电路,当控制信号M=0时它将两个输入四位二进制数相加,而M=1时,它将两个四位二进制数相减。允许附加必要的门电路。74LS283的框图如图3.2.22所示。

图12.7所示是由分立元件组成的最简单的门电路。A和B为输入,F为输出,输入可以是低电平(在此为0V),也可以为高电平(在此为3V),试列出状态表,分析它们各是哪一种门电路。