更多“n个输入端的二进制译码器,共有______输出端,对于每一组…”相关的问题

更多“n个输入端的二进制译码器,共有______输出端,对于每一组…”相关的问题

第2题

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

第3题

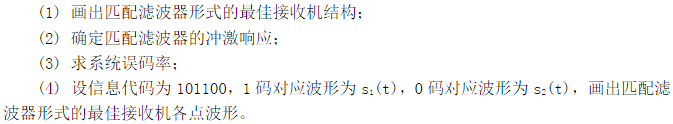

设到达接收机输入端的二进制信号码元为s1(t)及s2(t),如图中所示,输入端高斯噪声为n(t),功率谱密度为n0/2(W/

设到达接收机输入端的二进制信号码元为s1(t)及s2(t),如图中所示,输入端高斯噪声为n(t),功率谱密度为n0/2(W/Hz)。

第4题

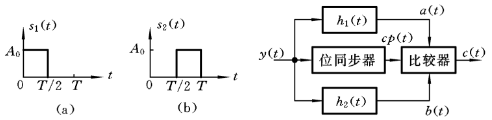

画出用两片4线-16线译码器74LS154组成5线-32线译码器的接线图。图4.11.1是74LS154的逻辑框图,图中的S'A、

画出用两片4线-16线译码器74LS154组成5线-32线译码器的接线图。图4.11.1是74LS154的逻辑框图,图中的S'A、S'B是两个控制端(亦称片选端),译码器工作时应使S'A和S'B同时为低电平。当输入信号A3A2A1A0为0000~1111这16种状态时,输出端从Y'0到Y'15依次给出低电平输出信号。

第8题

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。 要求:(1)根

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。

要求:(1)根据题意要求,写真值表。

(2)写出电路输出函数的最简与或表达式。

(3)画出用3线—8线译码器74LS138芯片实现的电路。

第10题

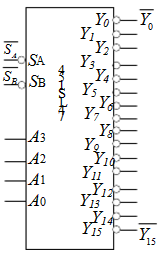

由3线-8线译码器CT74LS138及8选1数据选择器CT74LS151组成电路如下图所示。X2X1X0及Z2Z1Z0为两个3位二进制数。

由3线-8线译码器CT74LS138及8选1数据选择器CT74LS151组成电路如下图所示。X2X1X0及Z2Z1Z0为两个3位二进制数。试分析电路的逻辑功能。

如果结果不匹配,请

如果结果不匹配,请