题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

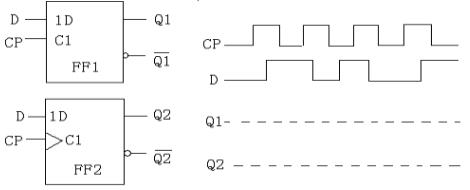

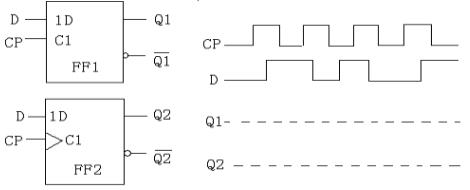

电路及输入波形如图所示,其中FF1是D锁存器,FF2是维持-阻塞D触发器,根据CP和D的输入波形画出Q1和Q2的输出波

电路及输入波形如图所示,其中FF1是D锁存器,FF2是维持-阻塞D触发器,根据CP和D的输入波形画出Q1和Q2的输出波形。设触发器的初态均为0。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

电路及输入波形如图所示,其中FF1是D锁存器,FF2是维持-阻塞D触发器,根据CP和D的输入波形画出Q1和Q2的输出波形。设触发器的初态均为0。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“电路及输入波形如图所示,其中FF1是D锁存器,FF2是维持-…”相关的问题

更多“电路及输入波形如图所示,其中FF1是D锁存器,FF2是维持-…”相关的问题

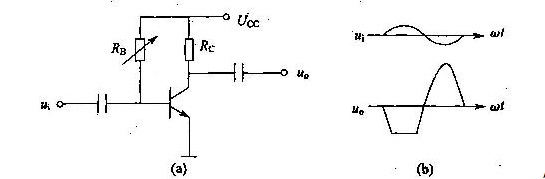

晶体管单管放大电路如图(a)所示,其中电阻RB可调,当输入ui、输出uo。的波形如图(b)所示时,输出波形()。

A.出现了饱和失真,应调大RB

B.出现了饱和失真,应调小RB

C.出现了截止失真,应调大RB

D.出现了截止失真,应调小RB

带续流二极管的单相半波可控整流电路如图所示,R=5Ω,L足够大,U2=220V,求触发延迟角α=30°时输出电压和电流的平均值Ud、Id,并画出ud、id、uVT、iVT和iVD的波形。

输入信号A的波形和CP的波形如图5-47所示,试画出该电路中触发器输出Q的波形(初始状态为0)。

L-R-C串联电路如图所示。假设作用在输入端的电压为ei(t)=Eisinωt。试求通过电阻R的稳态电流i(t)。

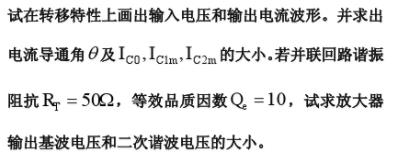

C类谐振功率放大器电路如图(a)所示,偏置VBB=0.2V,输入信号vi(t)=1.0cosωtV,回路调谐在输入信号频率上,电源电压VCC=20V。晶体管的转移特性曲线如图(b)所示,其中Von=0.7V。要求:

鉴频器输入调频信号us(t)=3cos[2π×106t+16sin(2×103t)]V,鉴频灵敏度SD=5mV/kHz,线性鉴频范围2△fmax=50kHz,试画出鉴频特性曲线及鉴频输出电压波形。

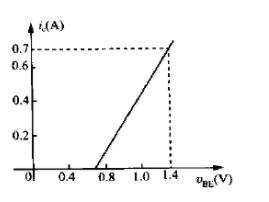

有一三抽头时域均衡器。各抽头增益分别为-1/3,1,1/4。若输入信号X(t)的抽样值为X-2=1/8,X-1=1/3,X0=1,X1=-1/4,X2=1/16,求均衡器输入及输出波形的峰值失真。

根据噪声系数定义

这与两级联噪声系数公式不同,错误在哪里?

由16×4位ROM和4位二进制加法计数器74LS161组成的脉冲分配电路如图7-13所示,ROM输入和输出关系如表7-4所示。试画出在CLK信号作用下D3、D2、D1、D0的波形。

表7-4 R0M输入和输出关系 | |||||||

| 地址输入 | 数据输出 | ||||||

| A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 1 0 0 0 0 1 1 1 1 1 0 0 0 0 0 0 | 1 0 0 1 1 0 0 0 1 1 0 0 0 1 1 0 | 1 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 | 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

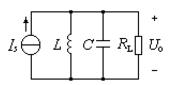

并联谐振回路L=10μH,C=300pF,均无损耗,负载电阻RL=5kΩ,电流IS=1mA,如图所示。求:

(1)回路谐振频率f0及通频带2f0.7;(2)当输入信号频率为fo时的输出电压;(3)若要使通频带扩大一倍,LC回路两端应再并联多大的电阻?