题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

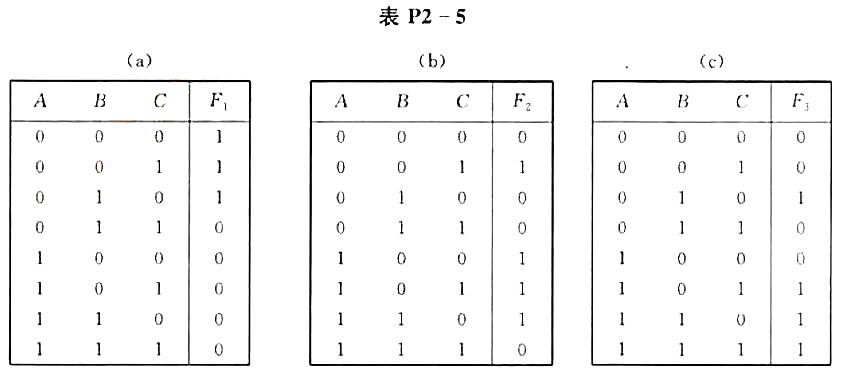

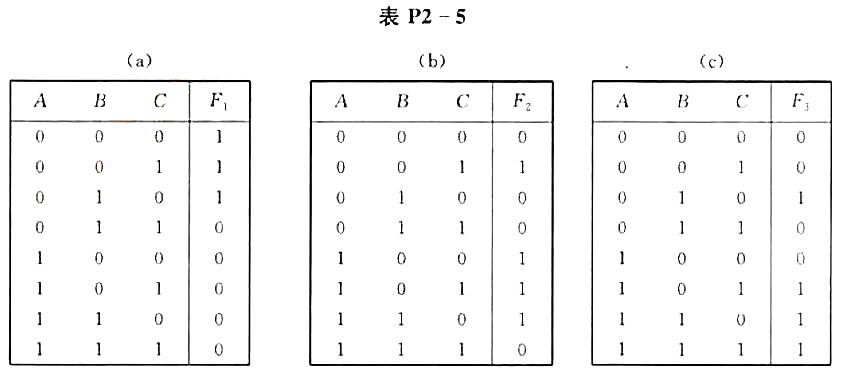

已知逻辑函数的真值表分别如表P2-5(a)、(b)、(c)所示。(1)试分别写出各逻辑函数的最小项之和表达

已知逻辑函数的真值表分别如表P2-5(a)、(b)、(c)所示。

(1)试分别写出各逻辑函数的最小项之和表达式、最大项之积表达式。

(2)分别求出各逻辑函数的最简与或式、最简或与式。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知逻辑函数的真值表分别如表P2-5(a)、(b)、(c)所示。

(1)试分别写出各逻辑函数的最小项之和表达式、最大项之积表达式。

(2)分别求出各逻辑函数的最简与或式、最简或与式。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知逻辑函数的真值表分别如表P2-5(a)、(b)、(c)所…”相关的问题

更多“已知逻辑函数的真值表分别如表P2-5(a)、(b)、(c)所…”相关的问题

已知逻辑函数的真值表如表2.4(a)、(b)所示,试写出对应的逻辑函数式。

| 表2.4(a) | |||

| A | B | C | Y |

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 1 1 0 1 0 0 0 |

| 表2.4(b) | ||||

| M | N | P | Q | Z |

| 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 | 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 | 0 0 0 1 0 0 1 1 0 0 0 1 1 1 1 1 |

已知逻辑函数Yl和Y2的真值表如表P2.9(a)和(b)所示,请写出Yl和Y2的逻辑函数式。

| 表 P2.9(a) | ||||||||||||||||||||

|

| 表 P2.9(b) | ||||||||||||||||||||||||||||||||||||

|

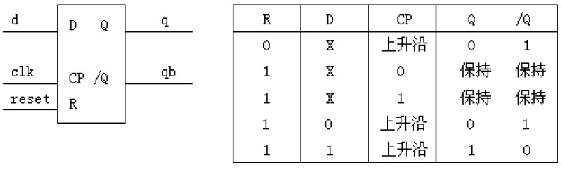

用VHDL语言描述带同步置位/复位端的D触发器(如图3-5所示,真值表如表3-3所示)的逻辑功能。

| 表3-3 带同步置位/复位端的D触发器的真值表 | |||||

| S | R | D | CLK | Q | Q' |

| 0 1 1 1 1 | 1 0 1 1 1 | × × × 0 1 | 上升沿 上升沿 0 上升沿 上升沿 | 1 0 保持 0 1 | 0 1 保持 1 0 |

已知线性规划问题

minz=-2x1+x2-x3

用单纯形法求得最终表如表2-13所示。试用灵敏度分析的方法分别判断以下情况时的最优解。

表2-13

|

(1)目标函数系数中的c2=1以c2=-3代替;

(2)目标函数系数中的c1=-2以c1=0代替;

(3)约束条件右端项由变为

时上述最优解的变化;

(4)引人一个新的约束:-x1+2x2≥2。

列出下列逻辑函数的真值表。

(1)Y1=A'B+BC+ACD';

(2)Y2=A'B'CD'+(B C)'D+AD。

C)'D+AD。