题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

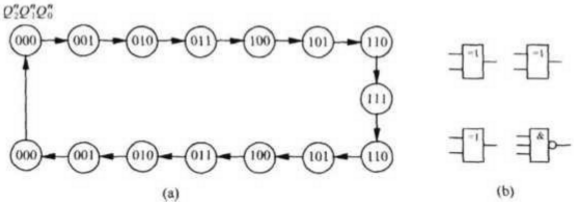

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求

用集成电路芯片74LS161设计一个计数器,自动完成3位二进制加/减循环计数,状态转换图如图T9.4-1(a)所示,要求只能用三个2输入异或门和一个3输入与非门实现,如图T9.4-1(b)所示。

提示:将74LS161的输出作为输入变量,3位二进制加/减循环计数器的状态作为输出变量,列出状态转换真值表,其中状态1000不用,并用端作为加/减转换控制。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用集成电路芯片74LS161设计一个计数器,自动完成3位二进…”相关的问题

更多“用集成电路芯片74LS161设计一个计数器,自动完成3位二进…”相关的问题

。当

。当