题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

由4位比较器74LS85和4位二进制计数器74161构成的定时电路,如图7.2.1所示。Z为输出端,设比较器的输

入端A3A2A1A0接固定电平1001;计数器的数据输入端D3D2D1D0=0010。 (1)一个Z脉冲周期内包含多少个CP脉冲周期? (2)若将

1.jpg) 试求一个Z脉冲周期内应包含多少个CP脉冲周期。

试求一个Z脉冲周期内应包含多少个CP脉冲周期。

2.jpg)

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

1.jpg) 试求一个Z脉冲周期内应包含多少个CP脉冲周期。

试求一个Z脉冲周期内应包含多少个CP脉冲周期。

2.jpg)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“由4位比较器74LS85和4位二进制计数器74161构成的定…”相关的问题

更多“由4位比较器74LS85和4位二进制计数器74161构成的定…”相关的问题

设有一个4位二进制数X,送到一个判别电路。要求:①当4≤X≤7时,输出YA=1②>X≤3时,输出YB=1③当X≥8时,输出YC=1。试用两片4位数字比较器74LS85与若干个逻辑门实现此判别电路。

用两片4位数值比较器74HC85实现三个4位二进制数A=A3A2A1A0,B=B3B2B1B0,C=C3C2C1C0的并行比较。要求给出“A最大”、“A最小”和“三个数相等”三个输出信号,必要时可用门电路。

用PAL16R6设计一个4位二进制计数器,要求:

(1)具有并行置数功能。并行数据输入为P0,P1,P2,P3,控制信号为

(2)具有加/减计数功能。控制信号为

(3)具有并行输出Q0,Q1,Q2,Q3。

(4)具有进位输出C和借位输出B。

A.由32位二进制数组成

B.每8位为一组,用小数点“.”分隔

C.每4位为一组,用小数点“.”分隔

D.每组用相应的十进制数(0-255之间的正整数)表示

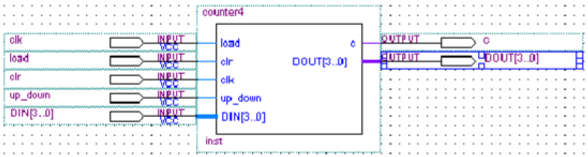

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。